# XMC\_3105 - Dual PCle x4 External PCI Express XMC Mezzanine

## Data Sheet XMC\_3105

#### **Features**

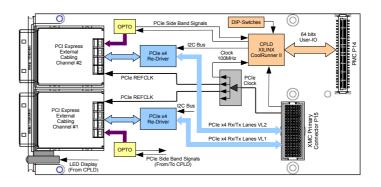

- Dual PCI Express x4 External cabling Standard Interface.

- Support for PCI Express cabling Upstream and Downstream connections.

- OPTO coupler isolation for PCI Express cabling sideband signals.

- PCIe x4 GEN1 & GEN2

Re-Driver with Equalization / Emphasis

configurable by strap & I2C Bus

- DIP-Switches for setting static options through XILINX CoolRunner II CPLD control.

- PCI Express Clock Re-Driver with very low jitter, low skew & low power.

- CPLD logic for XMC sideband signals and front panel dual Bi-color LED display.

- Optional PMC-Pn4 connector for User defined Back-IO LVTTL connections.

March 2011 - rev.A0

#### **Overview**

IOxOS Technologies introduces the XMC3105 mezzanine to extend the number of PCI Express External cabling interface for its PEV1100, IPV1102 and IFC1201 PCI Express Intelligent VME64X PMC/XMC Carrier platforms.

This PCI Express External cabling extension allows to build easily different PCI Express system architectures like Multi-PCIe x4 Branches for connecting more VME 64X Chassis or to build PCI Express Intelligent Switch for up to 4 PCI Express channels in a single slot VME64X industrial 6U form factor

#### **XMC Mezzanine**

The XMC3105 mezzanine complies with ANSI/VITA 42.3-2006 and ANSI/VITA 42.0-2008 specifications. It is designed to fit a single width XMC mezzanine form factor and implements the XMC-P15 connector for the dual PCI Express x4 Lanes and the 3.3V power (XMC-P16 is not implemented). The optional PMC/XMC P14 connector could be implemented for LVTTL user-defined Back-IO trough CPLD programming.

#### **Environment**

- Commercial temperature grade 0 to 50 °C

- Designed for Air-Cooled System

- XMC 3.3Volts/1.2A Power Supply requirement

### **PCI Express External Cabling**

The XMC3105 mezzanine implements 2 independent PCIe x4 standard connectors full compliant with the PCI Express External Cabling Rev.2.0 PCI-SIG specification.

Each PCle x4 channel implements sideband signals for both Upstream and Downstream Subsystem connection. The selection is performed for each channel by DIP-Switches setting that configure the related CPLD logic. OPTO coupler isolation and Open-Drain drivers are automatically configured for Upstream and Downstream Subsystems.

#### **PCI Express Re-Driver**

The XMC3105 mezzanine implements PERICOM PCI Express GEN2 Re-Driver for each channel to provide Equalization and Emphasis amplifier for supporting short and long PCI Express External cabling up to 7 meters. The configuration of these PCIe x4 Re-drivers is assumed by the CPLD logic trough simple DIP-Switch setting. At the Power-ON, the CPLD will configure trough the I2C Bus each PCIe Re-Driver according programmed modes selected by the DIP-Switches.

Dip-Switches setting Mode for:

- Rx Equalization Level from 0 to 12.3 dB

- Tx Emphasis Level from 0 to -8.5 dB

- Tx Output Swing from 0.5 to 1.0 Volt

4, chemin de Fontenailles 1196 Gland SWITZERLAND tel: +41 22 364 76 90

Email: info@ioxos.ch

### **Ordering Information**

| Article Reference | Product Description                                             |

|-------------------|-----------------------------------------------------------------|

| XMC3105-A0        | Dual PCI Express x4 External Cabling XMC single width mezzanine |

© 2011 IOxOS Technologies SA All rights reserved

IOxOS Technologies SA - Chemin des Fontenailles 4, 1196 Gland, Switzerland Tel: +41 22 364 76 90 Fax: +41 22 364 76 94 www.ioxos.ch